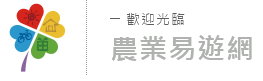

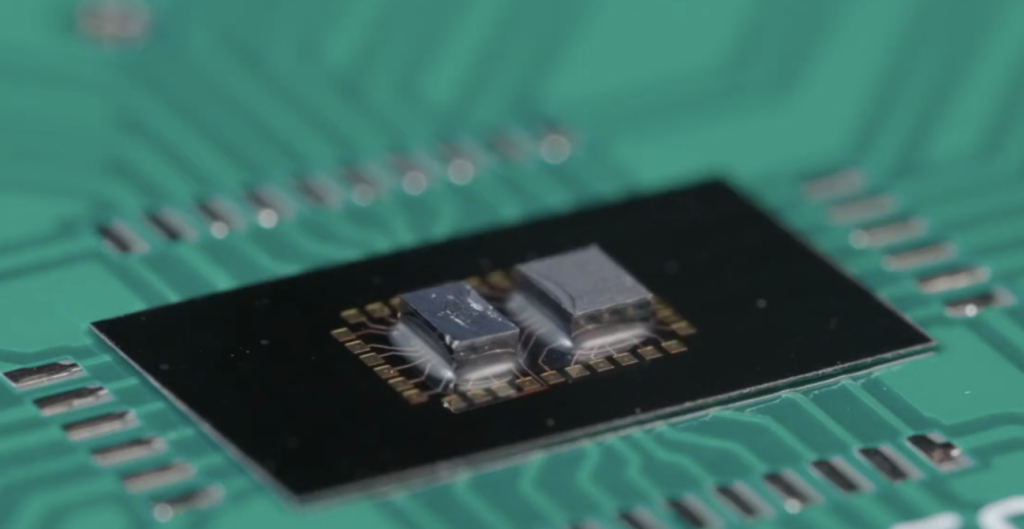

▲氮化鎵開關電路晶片模組。(圖/國研院提供)

【勁報記者羅蔚舟/竹科報導】

在全球半導體正式邁入後摩爾定律時代、人工智慧(AI)與高效能運算(HPC)需求急遽攀升的關鍵時刻,先進封裝已成為決定科技競爭力與產業布局的關鍵核心技術。國家實驗研究院台灣半導體研究中心(國研院半導體中心)1/13日發表「晶片級先進封裝研發平台」,將協助推動臺灣半導體產業從「製程領先」,邁向「系統整合與應用創新領先」的新階段,為後摩爾時代奠定關鍵競爭優勢。

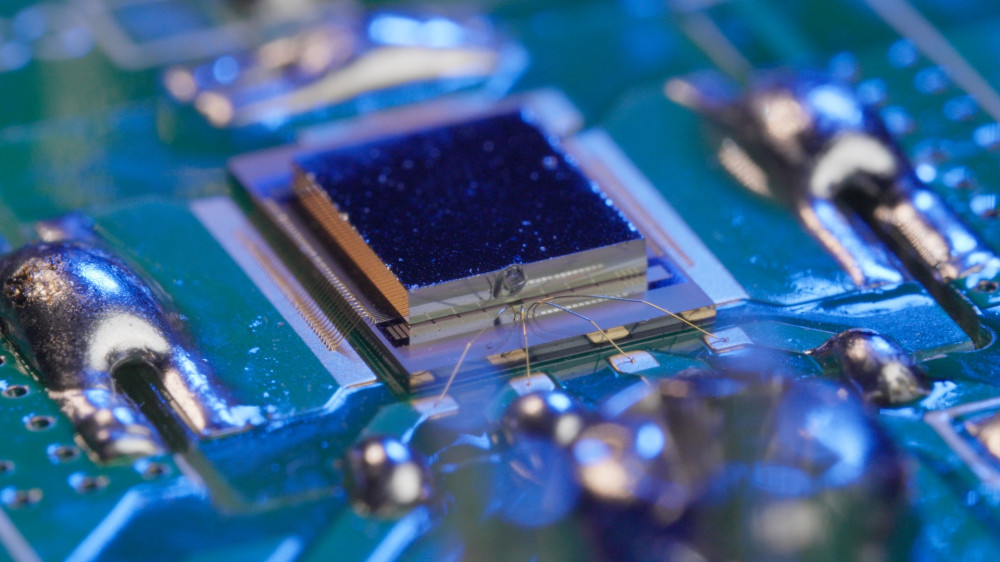

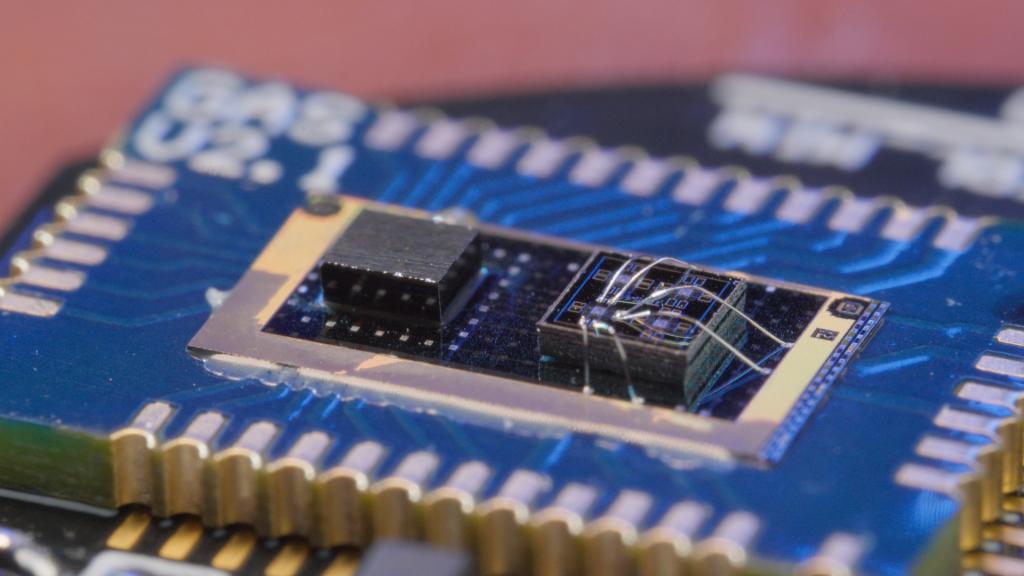

▲矽光子EICPIC光纖整合電路模組。(圖/國研院提供)

國科會主委兼國研院董事長吳誠文表示,未來的AI應用,需要更高效能、更高密度、同時更低功耗的晶片解決方案,挑戰前所未有,但機會也同樣巨大。這個關鍵機會,就是「先進封裝技術」,這是串連「晶片到系統、創意到產品」的價值鏈樞紐,更是推動AI新十大建設中矽光子、量子電腦與智慧機器人等關鍵技術不可或缺的基石。「先進封裝技術」不只是下一代半導體競爭的核心戰場,更將決定臺灣未來的科技領導地位。在這個關鍵時刻,國研院半導體中心開發的「晶片級先進封裝研發平台」,不僅為臺灣產學研界提供全球獨特的晶片級先進封裝研發能力,更將催生一個屬於臺灣的「先進封裝創新生態系」,加速前瞻實體AI技術的落地與商業化,帶動百工百業升級。

▲高解析數位/類比轉換器與類比/數位轉換器。(圖/國研院提供)

█先進封裝:延續摩爾定律的關鍵引擎

隨著製程微縮逐漸逼近物理極限,傳統以單一大型晶片為核心的系統單晶片(SoC)設計,已難以全面回應AI與HPC對於高速運算、超高頻寬與低功耗的需求。雖然SoC具備高度整合與低功耗優勢,但在效能擴展、晶片內傳輸距離、功耗管理、良率與成本,以及系統架構彈性等方面,逐漸顯露瓶頸。

因此,以異質整合為核心的先進封裝技術應運而生。透過將處理器、記憶體、高速傳輸等不同功能的小晶片(chiplet),如同樂高積木般進行3D封裝整合,可依功能選擇最合適的製程,不僅有效提升良率、降低成本,更能大幅提升系統運算效能、頻寬與能源效率,同時保有高度模組化與未來擴充彈性,成為延續摩爾定律的關鍵路徑。

▲氣體感測器溫控讀取模組。(圖/國研院提供)

█國研院半導體中心的關鍵突破:晶片級先進封裝研發平台

目前全球量產最先進的封裝技術之一為台積電的CoWoS(Chip-on-Wafer-on-Substrate),透過中介層晶圓與基板,實現運算晶片與高頻寬記憶體的高密度整合。然而,基板層的存在,也帶來成本、訊號傳輸距離與製程複雜度的挑戰。

國研院半導體中心此次發表的「晶片級先進封裝研發平台」,展現具國際前瞻性的關鍵突破,創新提出去除基板的 CoCoB(Chip-on-Chip-on-Board)封裝架構。該技術省略傳統基板,直接將中介層晶片與電路板連接,其難度猶如將一片很大片的鋼化玻璃,放置於鋪滿鵝卵石的地面上,卻仍需確保每一個接觸點都能精準連接。半導體中心透過在每一微小連接球下方導入可流動介面材料,成功克服不平整問題,使所有連接點皆能可靠接合。

此CoCoB技術具備兩大優勢:一是大幅縮短訊號傳輸路徑,顯著提升整合密度與系統效能;二是降低基板成本與製程複雜度,特別適合學研單位與新創團隊進行高彈性、低成本的異質整合實驗。產業界認為這種「去除基板」的封裝架構,將是下一代AI晶片的重要發展方向,也進一步驗證國研院半導體中心CoCoB技術的前瞻性與戰略價值。

█打通產學研任督二脈,驅動下一場AI矽革命

長期以來,全球先進封裝產能供不應求,使學研界與新創團隊難以取得最前沿的封裝資源。國研院半導體中心此次建置的「晶片級先進封裝研發平台」,正是以國家級科研能量,補上臺灣半導體創新體系中最關鍵的一塊拼圖。

此一開放式研發平台,不僅能支援HPC所需的處理器與高頻寬記憶體整合,也可高度整合生醫、環境感測、光電、電源管理等多元異質晶片,特別適合用於雛型驗證與前瞻應用開發。目前已吸引來自國內外16個教授研究團隊參與,包括臺大、清大、陽明交大、成大、中興、臺科大,以及美國史丹佛大學、加州大學、加拿大多倫多大學、德國慕尼黑工業大學等,投入AI運算、高頻通訊、感測、矽光子與電源晶片等多樣化晶片模組的設計與驗證。

整體而言,「晶片級先進封裝研發平台」展現四大核心價值:首先,在技術面,突破摩爾定律限制,結合感測與運算,打造實體 AI 與系統級創新的關鍵平台;其次,在經濟面,以「感測+封裝+系統整合」啟動新型態半導體創新模式;第三,在產業面,串聯產學研,加速前瞻技術落地與商業化;最後,在國際合作策略,提供學研單位對接國際頂尖技術,推動跨領域、跨國界的合作與發展。

國研院半導體中心表示,透過此平台的建置,臺灣將不再僅止於製程與單一晶片的競逐,而是正式邁向以系統整合與應用創新為核心的新世代半導體競賽,持續鞏固臺灣在全球半導體產業中不可或缺的關鍵地位。